## **Cortex-M Processors**

- Cortex-M processors use a load/store architecture with three basic types of instructions

- 1. Register-to-register operations for processing data

- 2. Memory operations which move data between memory and registers

- **3. Control flow** operations enabling programming language control flow such as if and while statements and procedure calls

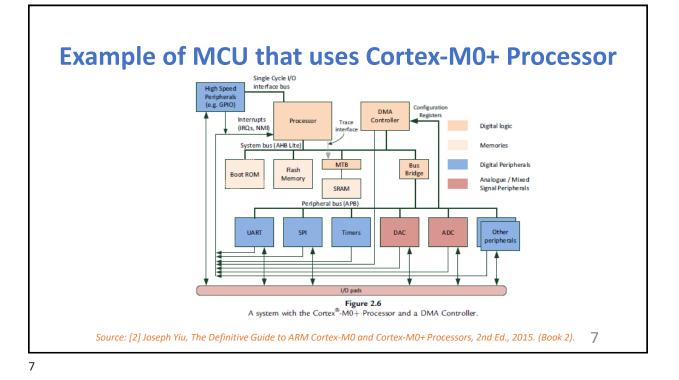

## **Cortex-M0+ Processor: Memory Addressing**

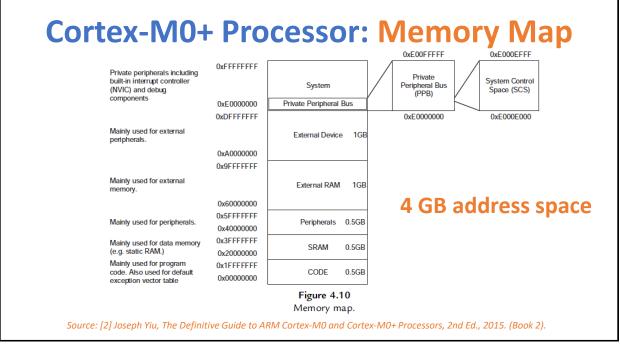

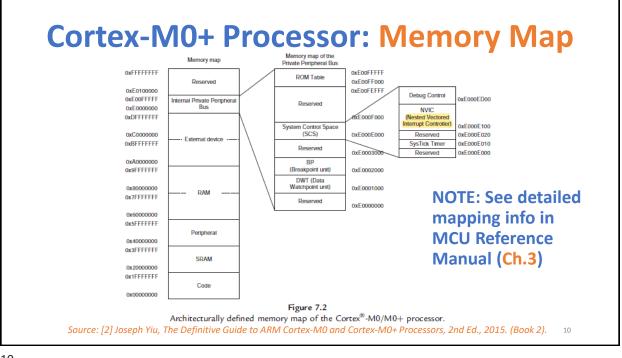

- 32-bit addressing supporting up to 4 GB of memory space.

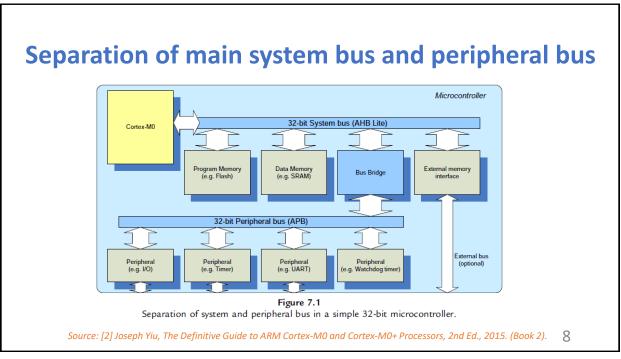

- The system bus interface is based on an on-chip bus protocol called (Advanced High-performance Bus) AHB-Lite, supporting 8-bit, 16-bit, and 32-bit data transfers.

- The AHB-Lite protocol is pipelined, support high operation frequency for the system.

- Peripherals can be connected to a simpler bus based on APB protocol (Advanced Peripheral Bus) via an AHB to APB bus bridge.

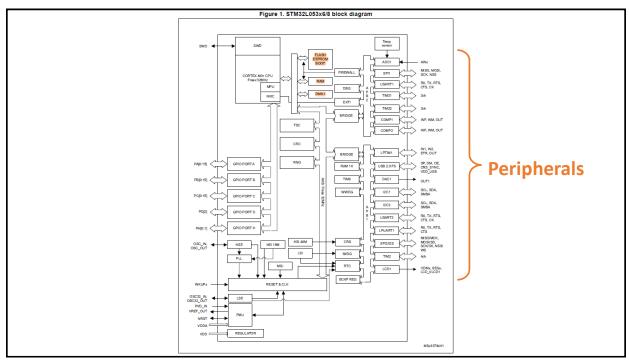

- Cortex-M0+ processor does not contain memories and peripherals (chip designers need to add these components to the MCU designs).

| STM32L053R8 -<br>Datasheet | Ultra-low-power 32-bit MCU Arm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>132L053C6 STM32L053C8</b><br><b>132L053R6 STM32L053R8</b><br><sup>(®</sup> -based Cortex <sup>®</sup> -M0+, up to 64KB<br>B EEPROM, LCD, USB, ADC, DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

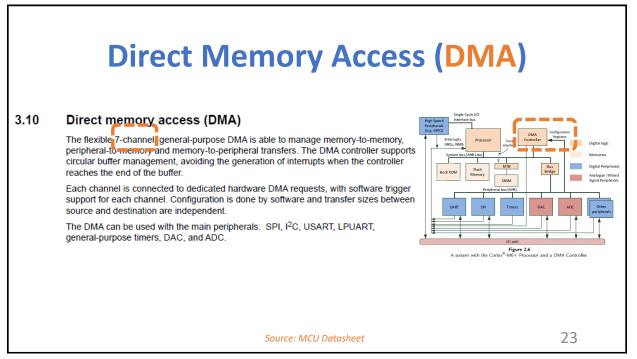

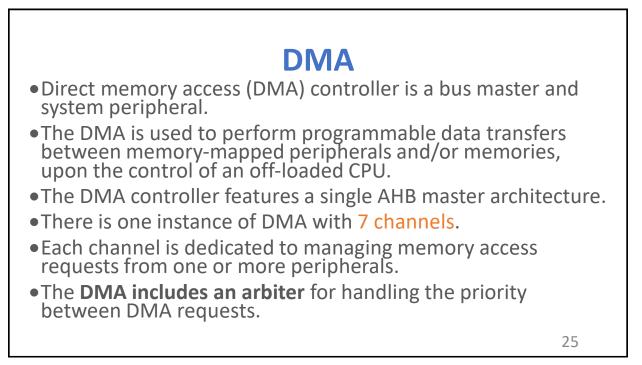

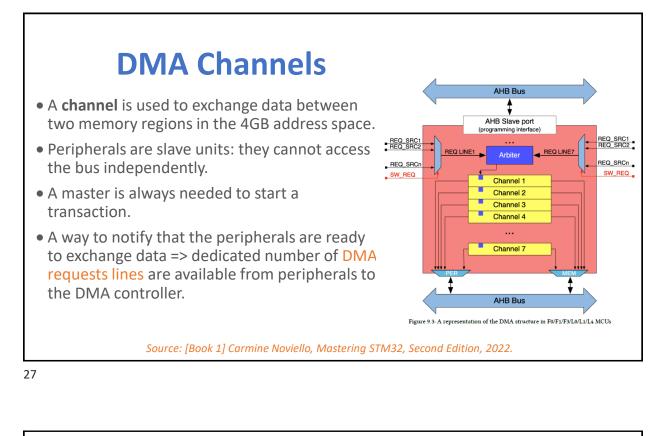

|                            | <ul> <li>Features</li> <li>Ultra-low-power platform <ul> <li>1.65 V to 3.6 V power supply</li> <li>-40 to 125 °C temperature range</li> <li>0.27 µA Standby mode (2 wakeup pins)</li> <li>0.4 µA Stop mode (16 wakeup lines)</li> <li>0.8 µA Stop mode + RTC + 8-Kbyte RAM retention</li> <li>88 µA/MHz in Run mode</li> <li>3.5 µs wakeup time (from RAM)</li> <li>5 µs wakeup time (from Flash memory)</li> </ul> </li> <li>Core: Arm<sup>®</sup> 32-bit Cortex<sup>®</sup>-M0+ with MPU</li> <li>From 32 kHz up to 32 MHz max.</li> <li>0.5 DMIPS/MHZ</li> </ul> <li>Memories <ul> <li>Up to 64-Kbyte Flash memory with ECC</li> <li>8-Kbyte RAM</li> </ul></li> | <ul> <li>Datasheet - production data</li> <li>UGFP84 10x10 mm<br/>LGFP84 10x10 mm<br/>LGFP48 7x7 mm</li> <li>UFGFP48<br/>(7x7 mm)</li> <li>TFBGA84 5x5 mm</li> <li>Step-up converted on board</li> <li>Rich Analog peripherals         <ul> <li>12-bit ADC 1.14 Msps up to 16 channels (down to 1.65 V)</li> <li>12-bit 1 channel DAC with output buffers (down to 1.8 V)</li> <li>2x ultra-low-power comparators (window mode and wake up capability, down to 1.65 V)</li> <li>Up to 24 capacitive sensing channels supporting touchkey, linear and rotary touch sensors</li> <li>7-channel DMA controller, supporting ADC, SPI,</li> </ul> </li> </ul> |

|                            | - 2 Kbytes of data EEPROM with ECC     - 20-byte backup register    Sector protection against R/W operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>Periatine Divia controller, supporting ADC, SPI,<br/>I2C, USART, DAC, Timers</li> <li>8x peripheral communication interfaces</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                               | NUC           | LEO-L05                                                                                                                                                  | 3R8                    |    |

|-------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----|

| <ul> <li>Package p</li> </ul> | in count: 64  | pins                                                                                                                                                     |                        |    |

| •Flash men                    | nory size: 64 | KB                                                                                                                                                       | ion                    |    |

|                               | NUCLEO-XXYYRT | Description                                                                                                                                              | Example: NUCLEO-L452RE |    |

|                               | xx            | MCU series in STM32 Arm<br>Cortex MCUs                                                                                                                   | STM32L4 Series         |    |

|                               | YY            | STM32 product line in the series                                                                                                                         | STM32L452              |    |

|                               | R             | STM32 package pin count                                                                                                                                  | 64 pins                |    |

|                               | т             | STM32 Flash memory size:<br>- 8 for 64 Kbytes<br>- B for 128 Kbytes<br>- C for 256 Kbytes<br>- E for 512 Kbytes<br>- G for 1 Mbyte<br>- Z for 192 Kbytes | 512 Kbytes             |    |

|                               |               | Source: Board user mar                                                                                                                                   | nual                   | 12 |

| 3.8 | Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     | <ul> <li>The STM32L053x6/8 devices have the following features:</li> <li>8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced has matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).</li> <li>The non-volatile memory is divided into three arrays: <ul> <li>32 or 64 Kbytes of ombedded Flash program memory</li> <li>2 Kbytes of data EEPROM</li> <li>Information block comaming 32 user and factory options bytes plus 4 Kbytes of</li> </ul> </li> </ul> |  |  |  |  |

|     | system memory<br>The user options bytes are used to write-protect or read-out protect the memory (with<br>4 Kbyte granularity) and/or readout-protect the whole memory with the following options:<br>• Level 0: no protection<br>• Level 1: memory readout protected.<br>The Flash memory cannot be read from or written to if either debug features are                                                                                                                                                                                                                               |  |  |  |  |

|     | <ul> <li>connected or boot in RAM is selected</li> <li>Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|     | The firewall protects parts of code/data from access by the rest of the code that is executed<br>outside of the protected area. The granularity of the protected code segment or the non-<br>volatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the<br>volatile data segment (RAM).                                                                                                                                                                                                                                                                       |  |  |  |  |

|     | The whole non-volatile memory embeds the error correction code (ECC) feature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|     | Source: MCU Datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

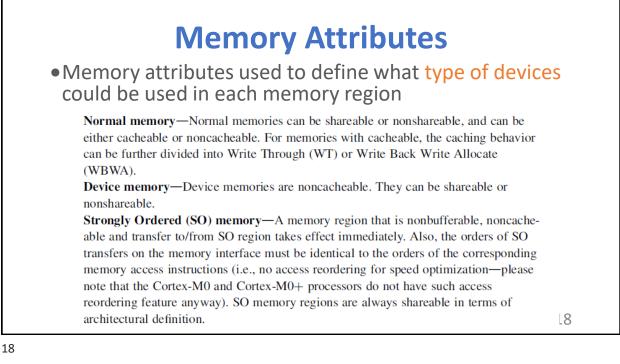

- •To make porting of software between different devices easier, a number of memory attribute settings are available for each regions in the memory map.

- •Memory attributes are characteristics of the memory accesses; they can affect data and instruction accesses to memory as well as accesses to peripherals.

## **Memory Attributes**

**Executable**—The executable attribute defines whether program execution is allowed in that memory region. If a memory region is defined as nonexecutable, in ARM documentation it is marked as eXecute Never (XN).

**Bufferable**—When a data write is carried out to a bufferable memory region, the write transfer can be buffered, which means the processor can continue to execute next instruction without waiting for the current write transfer to complete.

**Cacheable**—If a cache device is present on the system, it can keep a local copy of the data during a data transfer, and reuse it next time the same memory location is accessed to speed up the system. The cache device can be a cache memory unit, or could be a small buffer in a memory controller.

Shareable—The shareable attribute defines whether a memory region can be accessed by more than one processor. If a memory region is shareable, the memory system needs to ensure coherency between memory accesses by multiple processors in this region.

| Address                   | Region     | Memory<br>type      | Cache | XN | Shareable | Descriptions                                                         |

|---------------------------|------------|---------------------|-------|----|-----------|----------------------------------------------------------------------|

| 0x00000000-<br>0x1FFFFFFF | CODE       | Normal              | WT    | -  | _         | Memory for program code<br>including vector table                    |

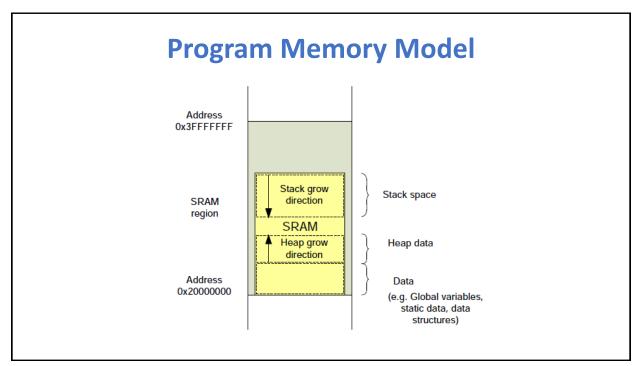

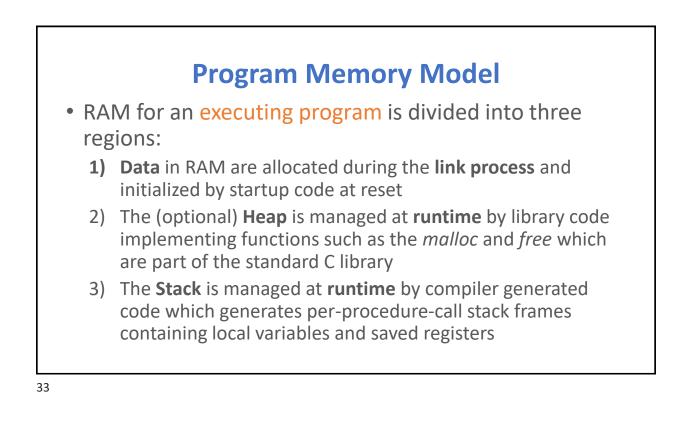

| 0x20000000-<br>0x3FFFFFFF | SRAM       | Normal              | WBWA  | _  | _         | SRAM, typically used for<br>data and stack memory                    |

| 0x40000000-<br>0x5FFFFFFF | Peripheral | Device              | -     | XN | _         | Typically used for on-chip<br>devices                                |

| 0x60000000-<br>0x7FFFFFFF | RAM        | Normal              | WBWA  | _  | _         | Normal memory with<br>Write Back, Write Allocate<br>cache attributes |

| 0x80000000-<br>0x9FFFFFFF | RAM        | Normal              | wт    | _  | _         | Normal memory with<br>Write Through cache<br>attributes              |

| 0xA0000000-<br>0xBFFFFFFF | Device     | Device              | -     | XN | 5         | Shareable device memory                                              |

| 0xC0000000-<br>0xDFFFFFFF | Device     | Device              | -     | XN | _         | Nonshareable device<br>memory                                        |

| 0xE0000000-<br>0xE00FFFFF | PPB        | Strongly<br>ordered | -     | XN | 5         | Internal Private Peripheral<br>Bus                                   |

| 0xE0100000-<br>0xFFFFFFFF | Reserved   | Reserved            | _     | _  | _         | Reserved (Vendor-specific<br>usage)                                  |

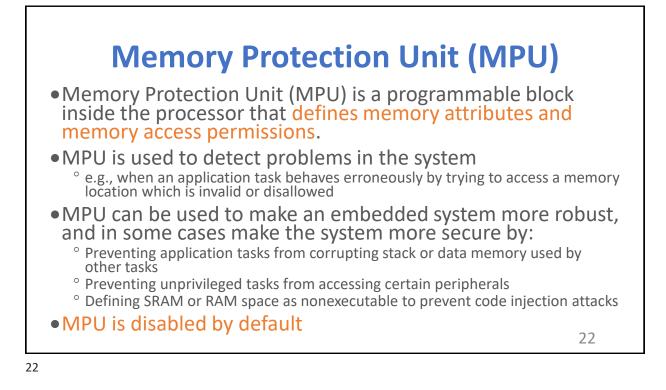

## **Memory access permission for regions**

#### Table 7.4: Memory access permission

| Memory region                                        | Default permission                                                                                                                     | Note                                                            |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| CODE, SRAM, Peripheral,<br>RAM, Device               | Accessible for both privileged<br>and unprivileged code.                                                                               | Access permission can be<br>overridden by MPU<br>configurations |

| System Control Space<br>including NVIC, MPU, SysTick | Accessible for privileged code<br>only. Attempts to access these<br>registers from unprivileged code<br>result in HardFault exception. | Cannot be overridden by MPU configurations                      |

Source: [2] Joseph Yiu, The Definitive Guide to ARM Cortex-M0 and Cortex-M0+ Processors, 2nd Ed., 2015. (Book 2). 20

|   | HAI                                   | L DM           | A Module                                          |        |

|---|---------------------------------------|----------------|---------------------------------------------------|--------|

|   | typedef struct {                      |                |                                                   |        |

|   | DMA_Channel_TypeDef                   | *Instance;     | /* Register base address                          | */     |

|   | DMA_InitTypeDef                       | Init;          | <pre>/* DMA communication parameters</pre>        | */     |

| • | HAL_LockTypeDef                       | Lock;          | /* DMA locking object                             | */     |

|   | IO HAL_DMA_StateTypeDef               | State;         | /* DMA transfer state                             | */     |

|   | void                                  | *Parent;       | /* Parent object state                            | */     |

|   | void                                  | (* XferCpltCal | lback)( <b>structDMA_HandleTypeDef</b> * hdma     | a);    |

|   | void                                  | (* XferHalfCpl | tCallback)( structDMA_HandleTypeDef *             | hdma); |

|   | void                                  | (* XferErrorCa | <pre>llback)( structDMA_HandleTypeDef * hdr</pre> | ma);   |

|   | IO uint32_t                           | ErrorCode;     | /* DMA Error code                                 | */     |

|   | <pre>} DMA_HandleTypeDef;</pre>       |                |                                                   |        |

|   | typedef struct {                      |                |                                                   |        |

|   | <pre>uint32_t Direction;</pre>        |                |                                                   |        |

|   | <pre>uint32_t PeriphInc;</pre>        |                |                                                   |        |

|   | <pre>uint32_t MemInc;</pre>           |                |                                                   |        |

|   | uint32_t PeriphDataAlignme            | ent;           |                                                   |        |

|   | <pre>uint32_t MemDataAlignment;</pre> |                |                                                   |        |

|   | uint32_t Mode;                        |                |                                                   |        |

|   | <pre>uint32_t Priority;</pre>         |                |                                                   |        |

|   | } DMA InitTypeDef;                    |                |                                                   | 20     |

|   | , <u> </u>                            |                |                                                   | 28     |

| (1) I                | Perform DMA Transfers in Polling Mode                                                                                                                                                              |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| We<br>1.<br>2.<br>3. | to setup the addresses on the memory and peripheral port;<br>to specify the amount of data we are going to transfer;<br>to arm the DMA;<br>to enable the DMA mode on the corresponding peripheral; |

| ° <b>H</b>           | t three points by using:<br>AL_StatusTypeDef HAL_DMA_Start();<br>rth point is peripheral dependent<br>29                                                                                           |

Γ

| (2)        | Perform DMA Transfers in Interrupt Mode                                                                                                                                                                                                                                                                          | I |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| •DM        | A can generate interrupts related to channel activities                                                                                                                                                                                                                                                          |   |

| • DM<br>1) | A can be enabled in interrupt mode following steps:<br>Define three functions acting as callback routines and pass them to function<br>pointers XferCplt-Callback, XferHalfCpltCallback and XferErrorCallback in a<br>DMA_HandleTypeDef handler (it is ok to define only the functions we are<br>interested in); |   |

| 2)         | Write ISR for the IRQ associated to the channel you are using and do a call to the HAL_DMA_IRQHandler() passing the reference to the DMA_HandleTypeDef handler;                                                                                                                                                  |   |

| 3)         | Enable the corresponding IRQ in the NVIC controller;                                                                                                                                                                                                                                                             |   |

| 4)         | Use function HAL_DMA_Start_IT(), which automatically performs all the necessary setup steps, passing to it same arguments of HAL_DMA_Start().                                                                                                                                                                    | у |

| •Exa       | mple 2                                                                                                                                                                                                                                                                                                           |   |

| ° So       | ee demo in class (also see Ch.9 of textbook) 31                                                                                                                                                                                                                                                                  |   |

| 31         |                                                                                                                                                                                                                                                                                                                  |   |

Γ

# **References & Credits**

- [Book 1] Carmine Noviello, Mastering STM32, Second Edition, 2022.

- [Book 2] Joseph Jiu, The Definitive guide to ARM Cortex-M0 and Cortex-M0+ Processors, 2015.

- <u>https://www.st.com/content/st\_com/en/arm-32-bit-</u> microcontrollers/arm-cortex-m0-plus.html

- STM32L053R8 MCU

- Datasheet

- User Manual

- NUCLEO-L053R8 Board

- User Manual

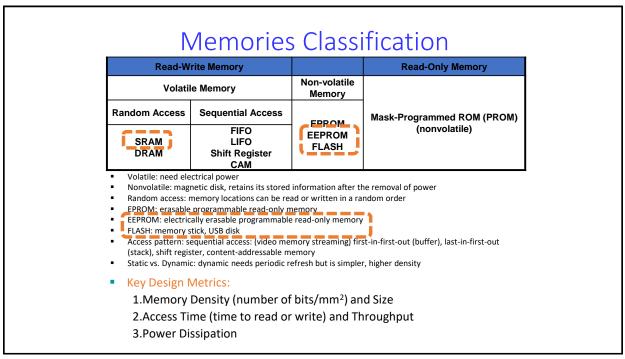

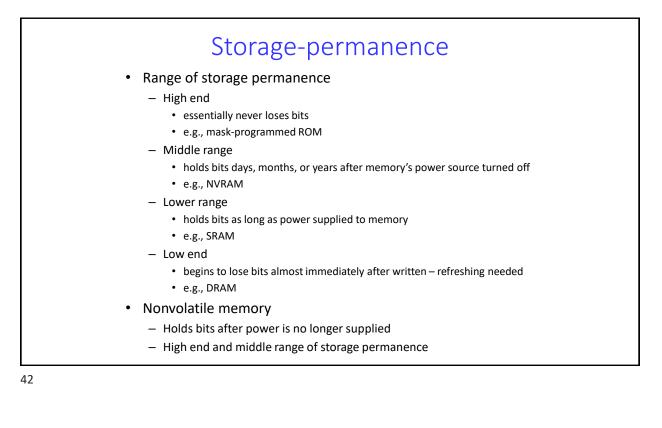

#### Memory Comparison Write Memory Volatility Read Density Power Rewrite Туре Speed Speed **SRAM** \_ \_ +++ +++ ++ DRAM + + - -++ -++ **EPROM** + \_ + + -**EEPROM** + + -+ + Flash + + + + +

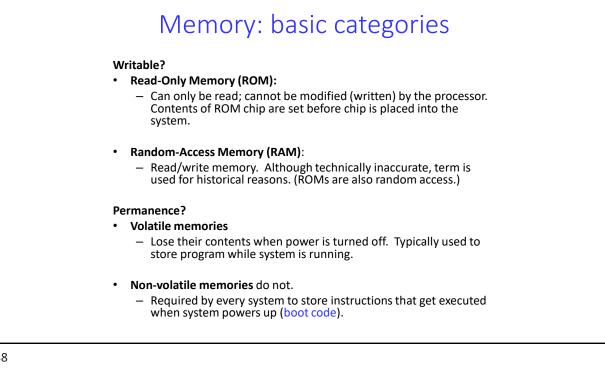

## **EEPROM**: Electrically erasable programmable ROM

- · Programmed and erased electronically

- typically by using higher than normal voltage

- can program and erase individual words

- Better write ability

- can be in-system programmable with built-in circuit to provide higher than normal voltage

- built-in memory controller commonly used to hide details from memory user

- writes very slow due to erasing and programming

- "busy" pin indicates to processor EEPROM still writing

- can be erased and programmed tens of thousands of times

- Similar storage permanence to EPROM (about 10 years)

- Far more convenient than EPROMs, but more expensive

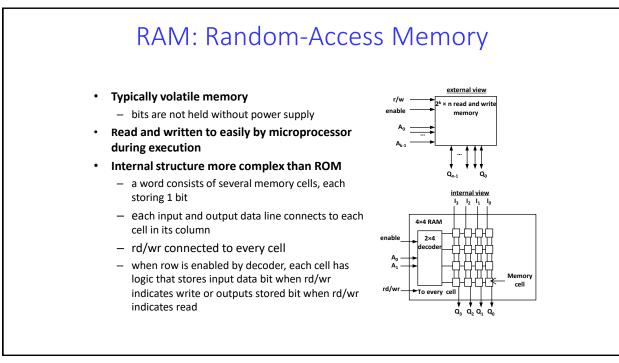

#### **Basic Types of RAM: SRAM vs. DRAM** Primary difference between different memory types is the bit cell SRAM Cell DRAM Cell raw enable addr raw select bit line bit line data bit line Larger cell $\Rightarrow$ lower density, higher Smaller cell $\Rightarrow$ higher density, lower cost/bit cost/bit Needs periodic refresh, and refresh No dissipation after read **Read non-destructive** Complex read $\Rightarrow$ longer access time No refresh required Special IC process $\Rightarrow$ difficult to Simple read $\Rightarrow$ faster access integrate with logic circuits Standard IC process $\Rightarrow$ natural for integration with logic