Research

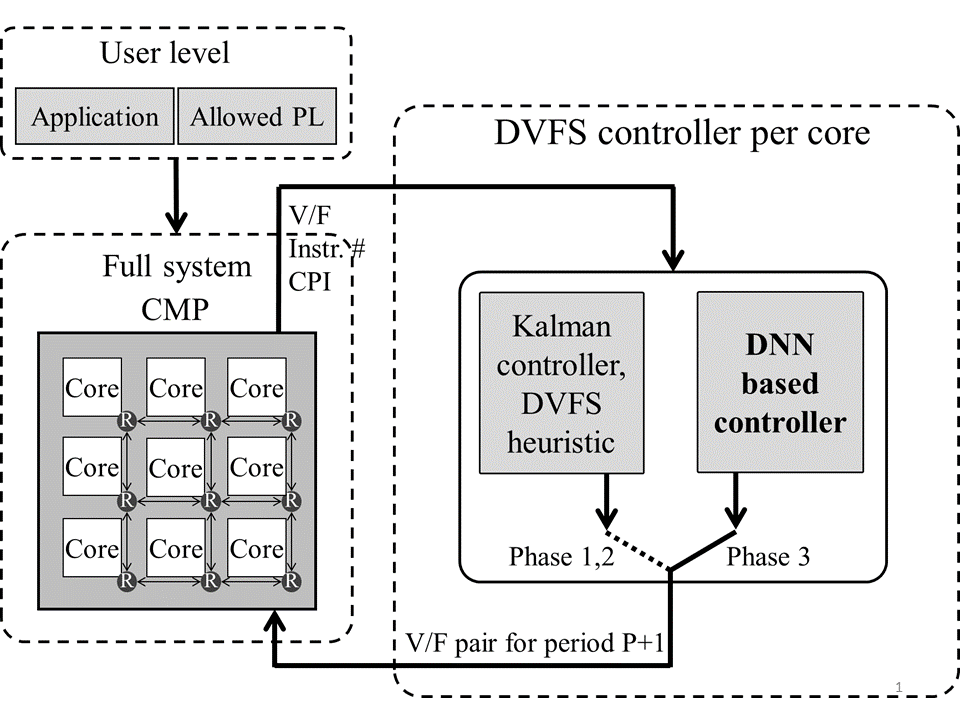

| 1) Machine learning based energy optimization

in multicore processors and datacenters. Background: Due to the evolution of the internet and the widespread of mobile devices, we interface computing continuously (e.g., e-mail, web search, social networks, etc.). A lot of these computations are performed in large datacenters with thousands of servers built with chip multiprocessors and which consume a lot of energy. Problem: Reduce energy consumption under given performance constraints in multicore processors. Solution: A dynamic energy management algorithm as a self-adaptive framework. Employ dynamic voltage and frequency scaling (DVFS) techniques. Use deep neural network (DNN) models for energy optimization under performance constraints in chip multiprocessors (CMPs). Funding/Support: We gratefully acknowledge and thank the generous support from the Dept. of Electrical and Computer (ECE) Engr. at Marquette University (MU). |

|

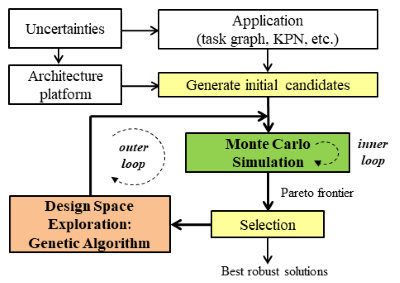

| 2) Uncertainty modeling

and design methods for embedded systems. Background: Due to technology downscaling, embedded systems have increased in complexity and heterogeneity. Increasingly large process, voltage, and temperature variations negatively affect the design and optimization process of these systems. These factors contribute to increased uncertainties that in turn undermine the accuracy and effectiveness of traditional design approaches. Problem: Uncertainty aware mapping for multicore embedded system platforms as a multi-objective optimization problem. Solution: Novel uncertainty modeling approaches and uncertainty-aware design methods for heterogeneous multicore embedded systems. Multi-objective design automation tool, which incorporates several algorithmic innovations based on Monte Carlo techniques and evolutionary algorithms. Funding/Support: We gratefully acknowledge and thank the generous support from the National Science Foundation (NSF). |

|

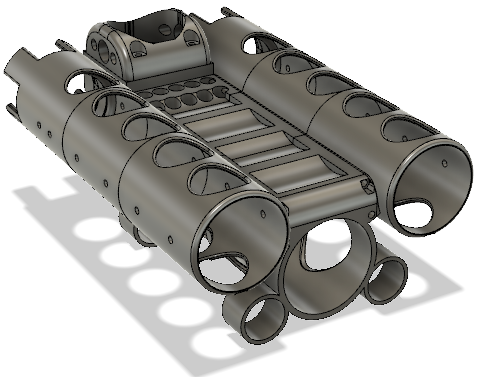

| (3) Underwater drones. Background: Underwater drones can be used for lake/river water quality monitoring and other water research projects. Problem: Develop cheap hardware/software of an underwater drone equipped with sensors for water quality monitoring. Solution: Build prototype #1 of remotely operated underwater drone. Funding/Support: We gratefully acknowledge and thank the generous support from the William and Nancy Stemper Endowed Faculty Scholars Fund for the Opus College of Engineering. Status: Currently recruiting MS student to work on this project. If interested, please contact me at cristinel.ababei AT marquette.edu |

|

| (4) LiDARs in intelligent transportation

systems. Background: When placed on a roadside, the LiDAR detection and tracking sensor can have many applications in traffic management. Examples of potential applications include: providing information about traffic approaching an intersection or a sharp curve, alerting connected users about road incidents and congestions, wrong-way vehicle detection and warning, and traffic signal actuation by means of lane-by-lane vehicle detection. Problem: Detect vehicles, pedestrians, and animals and estimate their speeds using LiDARs. Solution: Use a LeddarTech LiDAR sensor and implement embedded system-level solution. Status: Currently recruiting students to work on this project. If interested, please contact me at cristinel.ababei AT marquette.edu |

|

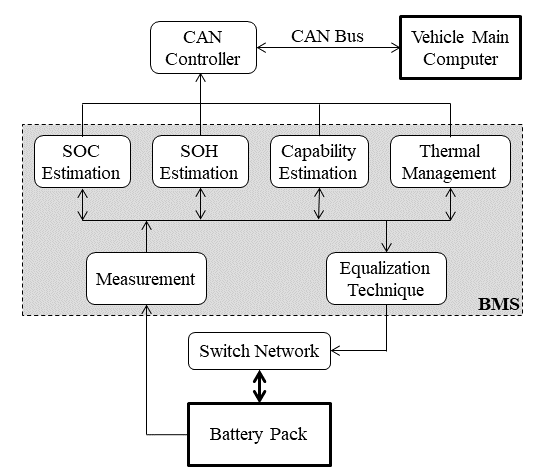

| (5) Simulation and optimization of vehicle

battery packs. Background: In hybrid-electric-vehicles, the role of the battery management system (BMS) is also to equalize cell voltages among other optimization tasks. To investigate such optimization algorithms, one can use full-system simulation tools. Problem: Cost effective state-of-charge estimation and cell balancing. Solution: Use in-house simulator and develop algorithm to control specific network of switches. Status: Currently recruiting students to work on this project. If interested, please contact me at cristinel.ababei AT marquette.edu |

|

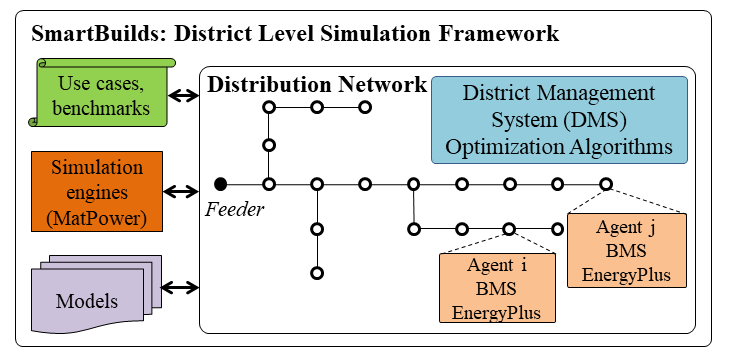

| 6) Energy and power simulation - smart buildings

and districts. Background: The building sector is the largest energy consumer in the world. For instance, buildings in the US account for more than 40 percent of the total energy consumption and greenhouse gas emissions. Therefore, it is economically, socially, and environmentally significant to increase the energy efficiency and to reduce the energy consumption of buildings. Problem: Scheduling of energy storage systems (batteries) to shift high cost energy consumption in order to reduce overall costs. Solution: Develop a district level simulation framework that allows to test and validate different district operation scenarios. These scenarios are identified through a set of optimization techniques that use energy storage systems - including batteries and thermal energy storage - placement, sizing, and operation scheduling such that the energy consumption and costs for the entire district and of each individual building are minimized. Funding/Support: We gratefully acknowledge and thank the generous support from the Mid-West Energy Research Consortium (M-WERC). |

|

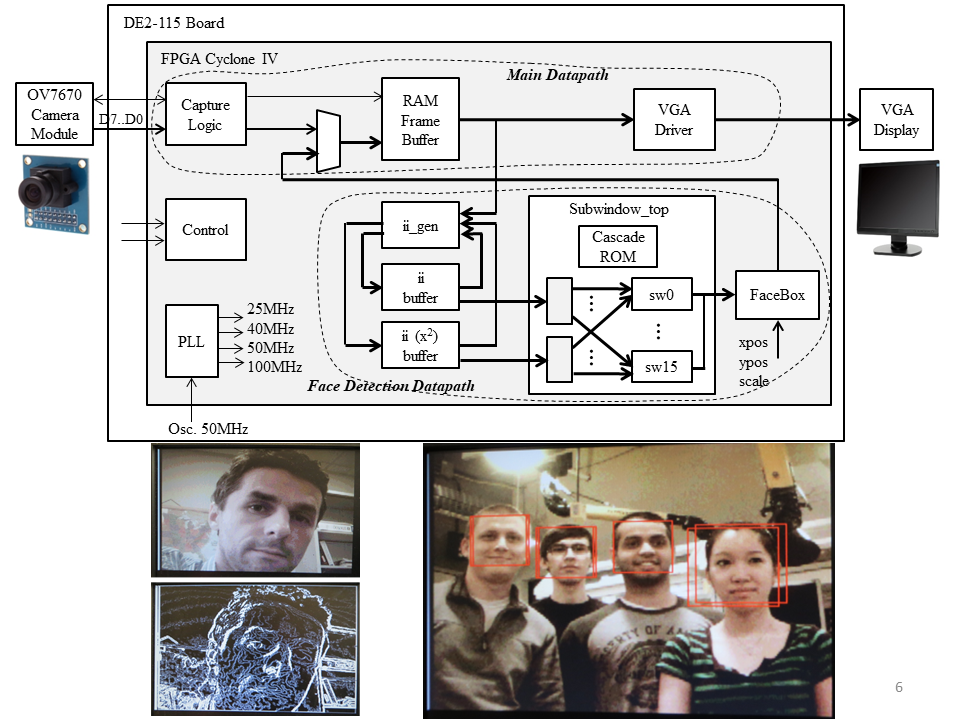

| 7) Field programmable gate arrays (FPGA) -

hardware accelerators. Background: Many applications today can benefit from faster execution times. Two of the most popular technologies used to speed up systems and software are FPGA (field programmable gate array) circuits and parallel computing techniques. FPGAs can be used as hardware accelerators in many application domains due to the hardware parallelism offered by these circuits. Problem: Exploit the parallelism offered by FPGAs to implement faster algorithms from various application domains. Solution: Complete implementations in FPGA hardware of face detection and edge detection algorithms, H.264 video decoding algorithm, and basic digital camera system. Complete description of these algorithms in VHDL (hardware description language) and verification on Intel Altera FPGA chips. Funding/Support: We gratefully acknowledge and thank the generous support from Intel Altera and from the OPUS College of Engr. at Marquette University (MU). |

|

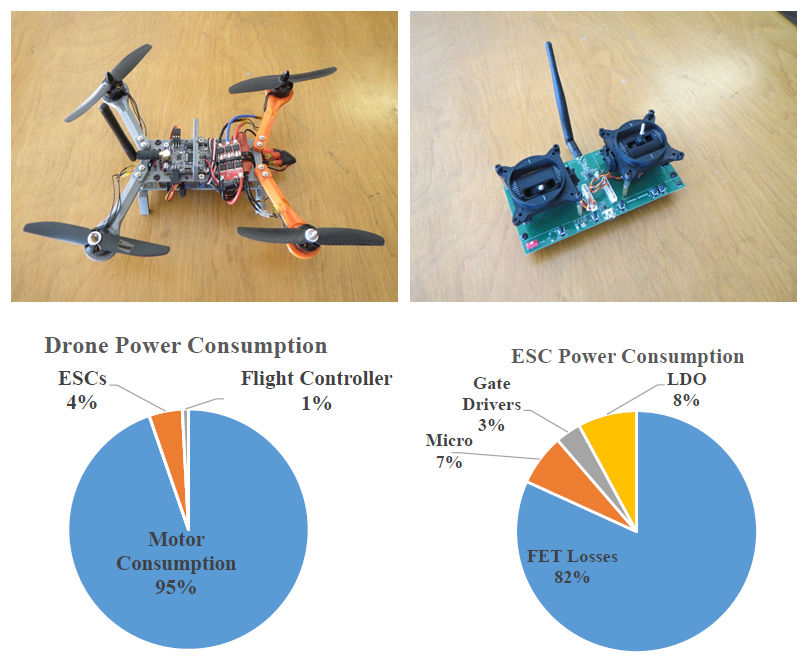

| 8) Aerial drone design -

power consumption. Background: Recently, aerial multi-rotor or drone systems have been applied in numerous applications such as surveillance, aerial photography, and other general consumer use. Problem: Short battery lifetime of currently available quadcopter drones is an issue that restricts the flying range. Solution: Design and prototype of in-house quadcopter and the study of factors that affect its energy consumption, which directly impacts the battery life and flight time. Better control algorithms to improve battery lifetime. New electronic speed controller designs. Funding/Support: We gratefully acknowledge and thank the generous support from the Dept. of Electrical and Computer (ECE) Engr. and from the OPUS College of Engr. at Marquette University (MU). |

|

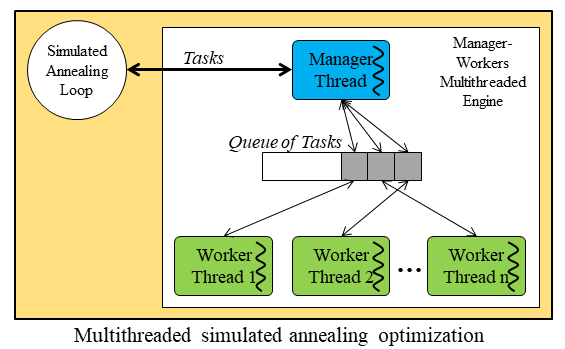

| 9) Parallel computing -

multithreading, CUDA programming. Background: To speed up computer programs, one can use parallel computing paradigms including: 1) Multithreading, which takes benefit of the multicore processors available today via concurrent execution of multiple tasks on different cores and 2) CUDA programming, which exploits the latest GPUs (graphics processor units) from NVIDIA to also execute concurrently programs in a multithreaded approach. Problem: Use parallel computing techniques to develop faster computer programs from various application domains. Solution: Use multithreading to speed-up the design space exploration using simulated annealing based optimization of patch antennas. Used multithreading to speed-up the placement step inside the automated design flow of FPGA circuits. Funding/Support: We gratefully acknowledge and thank the generous support from the OPUS College of Engr. at Marquette University (MU). |

|

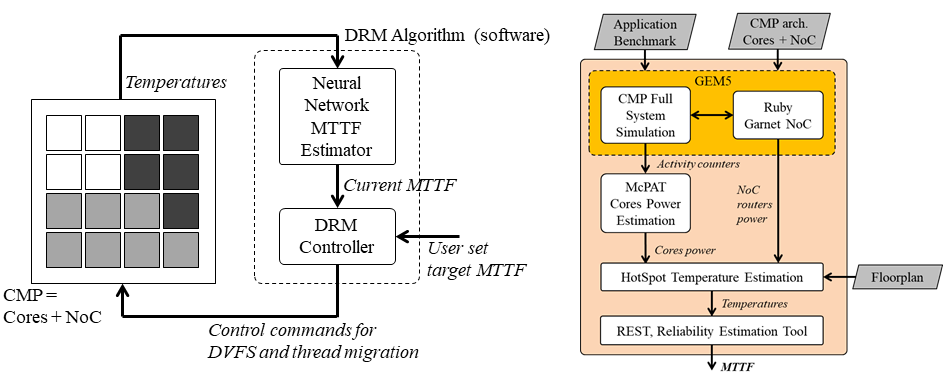

| 10) Reliability of

multicore processors. Background: Future integrated chip multiprocessors (CMPs) with hundreds of IP cores will contain billions of transistors and wires. Many transistors will be dead after manufacturing and the rest will be subject to the effects of wearout or aging mechanisms (e.g., electromigration, EM, thermal cycling TC, negative bias temperature instability, NBTI, time-dependent dielectric breakdown, TDDB), which will result in performance degradation and eventual device/system failure. Problem: Mitigate aging mechanisms in CMPs. Solution: Dynamic reliability management (DRM) algorithm that combines thread migration and dynamic voltage and frequency scaling (DVFS) as the two primary techniques to change the CMP operation. Funding/Support: We gratefully acknowledge and thank the generous support from the National Science Foundation (NSF) and from the OPUS College of Engr. at Marquette University (MU). |

|

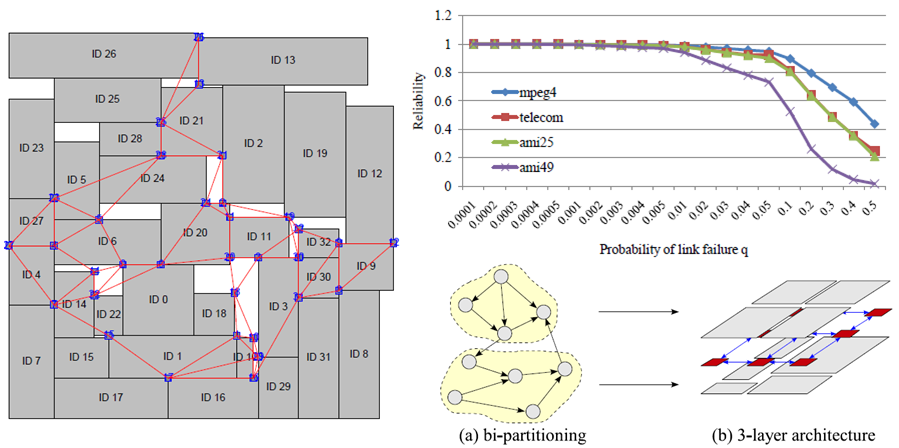

| 11) Networks-on-chip

(NoCs). Background: To address the "global interconnect delay problem" and to enable increased communication concurrency, network-on-chip (NoC) emerged as a promising new design paradigm for increasingly complex systems-on-chip (SoCs) and chip multiprocessors. Problem: NoC topology synthesis and optimization for reliability. Solution: Versatile software tool for efficient custom congestion aware NoC topology synthesis using multicommodity flow algorithm. New branch and bound algorithm for energy and reliability mapping for NoCs. New algorithm for fault tolerant NoC mapping. Exploration of new NoC architectural ideas including 3D integration. Funding/Support: We gratefully acknowledge and thank the generous support from the OPUS College of Engr. at Marquette University (MU). |

|

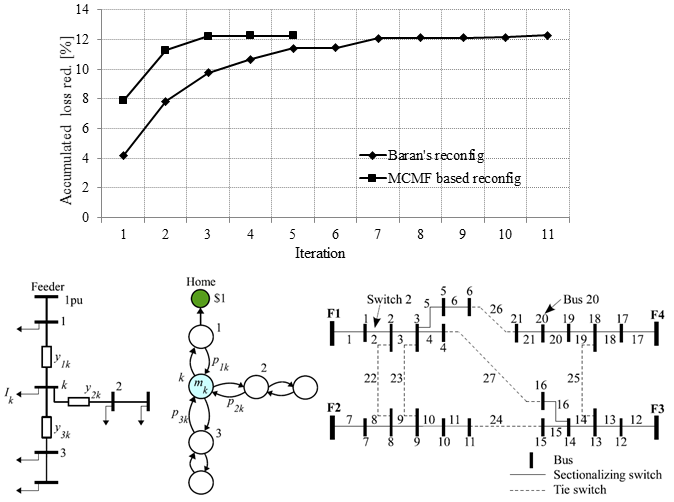

| 12) Power

distribution network reconfiguration. Background: Network reconfiguration of power distribution systems is defined as the change in the network structure as a result of closing tie and opening sectionalizing switches. It has been identified as a primary mechanism that has a direct impact on reliability, efficient service restoration and maintenance of optimal operating conditions. Problem: Distribution network reconfiguration for loss reduction. Solution: Efficient heuristic algorithm to solve the distribution network reconfiguration problem for loss reduction. We formulate the problem of finding incremental branch exchanges as a minimum cost maximum flow problem. This approach finds the best set of concurrent branch exchanges yielding larger loss reduction with fewer iterations, hence significantly reducing the computational runtime. Efficient random walks based technique for the loss estimation in radial distribution systems. The novelty of this approach lies in its property of localizing the computation. |

|

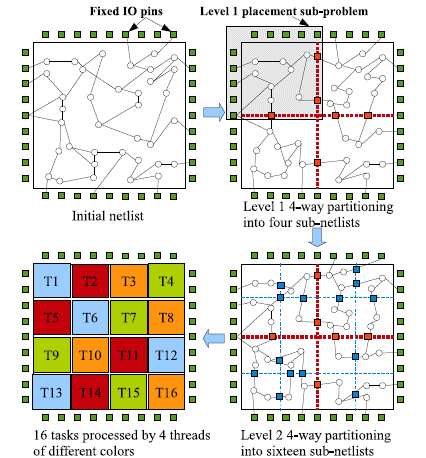

| 13) Electronic

design automation for VLSI and FPGA circuits. Background: Electronic design automation (EDA) deals with the development of specialized software tools used in the design of electronic systems (i.e., integrated circuits and printed circuit boards). This development encompasses electronic circuit design, microelectronic fabrication, graph theory, data structures, algorithm design, optimization, and programming (most often C/C++). The specialized software tools are used in a sequence of steps that form a flow or methodology that chip designers use to design and analyze entire semiconductor chips that can have billions of transistors. Therefore, EDA tools are essential for the design of these chips. Problem: Continue to develop improved EDA tools to address increasing chip size and complexity as well as new technologies such as 3D integration. Solution: Algorithmic innovations at the placement and routing steps in order to improve performance metrics such as delay and resource utilization for FPGA circuits as well as to reduce the computational runtime of these steps. |

|