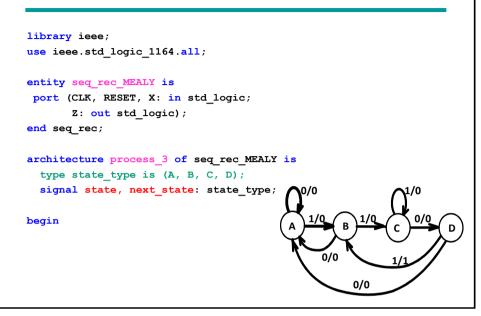

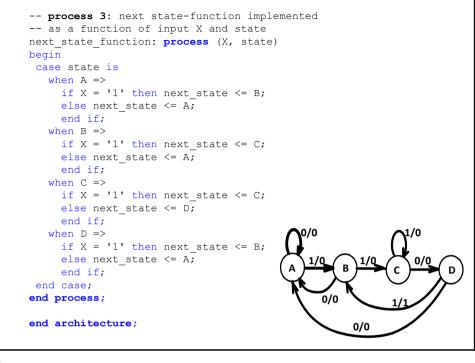

### VHDL code using 3 processes: sequential recognizer

```

-- process 1: implements positive edge-triggered

-- flipflop with asynchronous reset

state_register: process (CLK, RESET)

begin

if (RESET = '1') then

state <= A;

elsif (CLK'event and CLK = '1') then

state <= next state;</pre>

end if;

end process;

-- process 2: implement output as function

-- of input X and state

output function: process (X, state)

begin

case state is

when A => Z <= '0';

when B => Z <= '0';

when C => Z <= '0';

when D \Rightarrow if X = '1' then Z \ll '1';

В

else Z <= '0';</pre>

end if;

0/0

end case;

end process;

0/0

```

## 1. IF Statement

```

if CONDITION then

-- sequential statements

end if;

if CONDITION then

-- sequential statements

else

-- sequential statements

end if;

if CONDITION then

-- sequential statements

elsif CONDITION then

-- sequential statements

. . .

else

-- sequential statements

end if;

```

- Condition is a boolean expression

- Optional elsif sequence

- Conditions may overlap

- priority

- Optional else path

- executed, if all conditions evaluate to false

```

9

```

#### **Example 3** entity IFSTMT is port (A, B, C, X : in bit vector (3 downto 0); Z : out bit vector (3 downto 0)); end IFSTMT; architecture EX2 of IFSTMT is architecture EX1 of IFSTMT is begin begin process (A, B, C, X) process (A, B, C, X) begin begin if (X = "1111") then Z <= A; **if** (X = "1111") **then** Z <= B; **elsif** (X > "1000") **then** Z <= B; **elsif** (X > "1000") **then** Z <= C; Z <= C; else Z <= A; end if; end process; end if; end process; end EX1; end EX2;

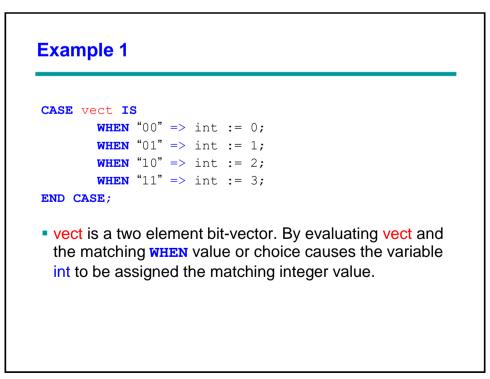

## 2. Case Statement

WHEN constant\_value => sequential statements

WHEN constant\_value => sequential statements

WHEN others => sequential statements

END CASE;

- The keyword WHEN is used to identify constant values that the expression might match. The expression evaluates a choice, and then the associated statements will be executed.

- The **CASE** statement will exit when all statements associated with the first matching constant value are executed.

#### Example 2: Clocked 4-to-1 MUX

```

ENTITY clocked mux IS

PORT ( inputs : IN BIT VECTOR (0 to 3);

: IN BIT_VECTOR (0 to 1);

sel

: IN BIT;

clk

output : OUT BIT);

END clocked mux;

ARCHITECTURE behave OF clocked_mux IS

BEGIN

PROCESS (clk)

VARIABLE temp : BIT;

BEGIN

CASE clk IS

WHEN '1' =>

CASE sel IS

WHEN "00" => temp := inputs(0);

WHEN "01" => temp := inputs(1);

WHEN "10" => temp := inputs(2);

WHEN "11" => temp := inputs(3);

END CASE;

output <= temp AFTER 5 ns;

WHEN OTHERS => NULL;

END CASE;

END PROCESS;

END behave;

```

15

#### **Example 3** entity CASE\_STATEMENT is port (A, B, C, X : in integer range 0 to 15; Z : out integer range 0 to 15; end CASE STATEMENT; architecture EXAMPLE of CASE STATEMENT is begin process (A, B, C, X) begin case X is when 0 => $Z \leq A;$ when 7 | 9 => $Z \leq B;$ when 1 to 5 => $Z \leq C;$ when others => Z <= 0; end case; end process; end EXAMPLE;

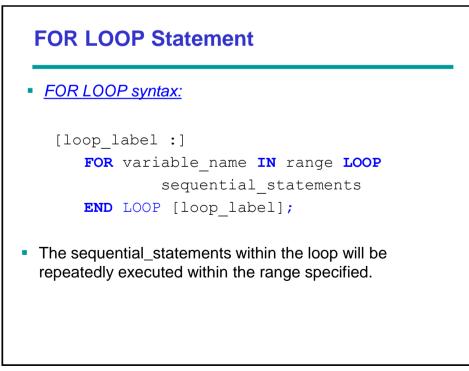

## Example

```

FOR i IN 0 to 3 LOOP

IF vect(i) = '1' THEN

value := value + 2**i;

ENDIF;

END LOOP;

```

- After the fourth pass, the loop range will be exceeded and the loop will terminate.

- A feature of VHDL: unlike most programming languages, the range variable i was not declared. Any range variable used within the FOR construct does not have to be declared. The same range identifier can be used repeatedly from one loop statement to the next.

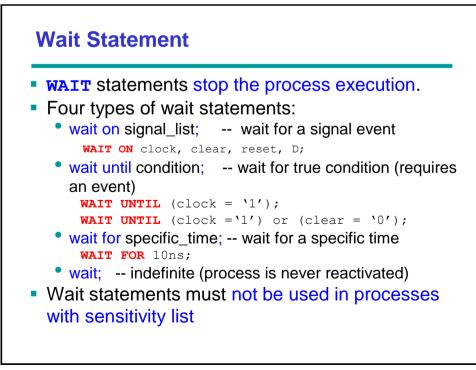

WAIT ON clock UNTIL (clear='0') FOR 10 ns;

- This is a combination of three types of WAIT statements. In this example, the wait statement will suspend the process and resume if:

- Simulation time has advanced 10 ns or

- There is an event on clock and

The Boolean expression clear = 0 is true

25

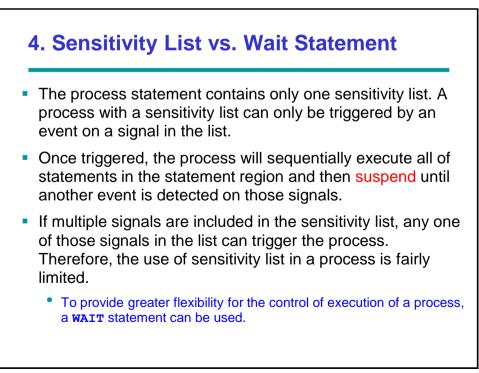

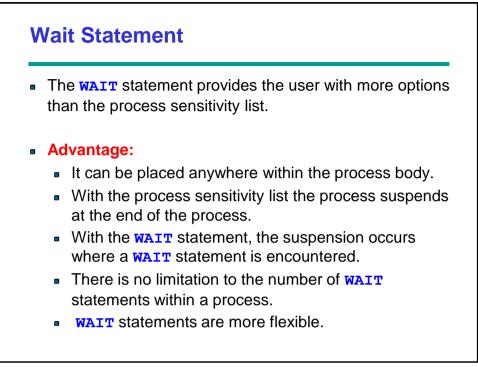

## **Sensitivity List & Wait Statement** A process with sensitivity is functionally equivalent to a process statement with a WAIT statement as the last statement within

A process with sensitivity is functionally equivalent to a process statement with a WAIT statement as the last statement within the process.

```

PROCESS (clk)

BEGIN

clk <= NOT (clk) AFTER 50ns;

END PROCESS;</pre>

```

```

PROCESS

BEGIN

clk <= NOT (clk) AFTER 50ns;

WAIT ON clk;

END PROCESS;</pre>

```

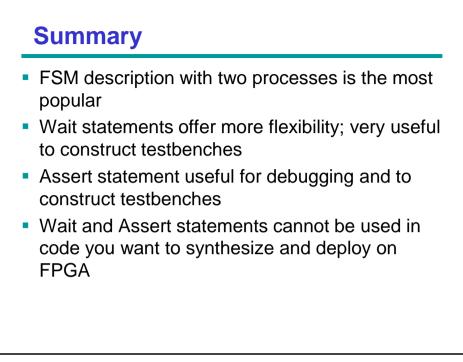

If a process does not have a sensitivity list and does not have a WAIT statement contained within it, the process will loop forever during initialization.

This is important to remember!

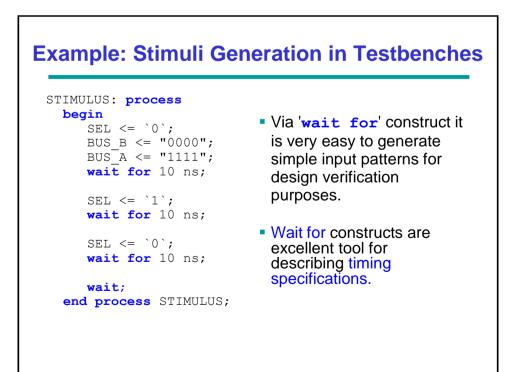

## **WAIT Statements and Behavioral Modeling**

```

READ_CPU : process

begin

wait until CPU_DATA_VALID = `1`;

CPU_DATA_READ <= `1`;

wait for 20 ns;

LOCAL_BUFFER <= CPU_DATA;

wait for 10 ns;

CPU_DATA_READ <= `0`;

end process READ_CPU;

```

- It is easy to implement a bus protocol for simulation.

- This behavioral modeling can only be used for simulation purposes as it is definitely not synthesizable!