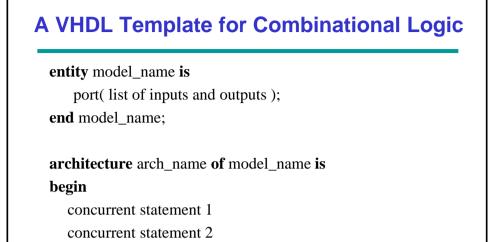

concurrent statement N;

end arch\_name;

...

| 2-to-4 Decoder                                           |                                         |

|----------------------------------------------------------|-----------------------------------------|

| LIBRARY ieee;                                            | $En w_1 w_0   y_3 y_2 y_1 y_0$          |

| USE ieee.std_logic_1164.all;                             |                                         |

|                                                          | 1 0 0 0 0 0 1                           |

| ENTITY dec2to4 IS                                        | 1 0 1 0 0 1 0                           |

| PORT (w : IN STD_LOGIC_VECTOR(1 DOWNTO 0);               |                                         |

| En: IN STD_LOGIC;                                        | 1 1 0 0 1 0 0                           |

| y : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );<br>END dec2to4 : | 1 1 1 1 0 0 0                           |

| END dec2i04;                                             | 0 x x 0 0 0 0                           |

| ARCHITECTURE dataflow OF dec2to4 IS                      |                                         |

| SIGNAL Enw : STD_LOGIC_VECTOR(2 DOWNTO 0);               |                                         |

| BEGIN                                                    | W                                       |

| $Enw \leq En \& w;$                                      | $\rightarrow$ $^{n_1}$ $^{y_3}$         |

| WITH Enw SELECT                                          | <i>w v</i>                              |

| y <= "0001" WHEN "100",                                  | $\rightarrow w_0  y_2 \rightarrow$      |

| "0010" WHEN "101",                                       | <i>y</i> .                              |

| "0100" WHEN "110",                                       |                                         |

| "1000" WHEN "111",                                       | $\rightarrow En \qquad y_0 \rightarrow$ |

| "0000" WHEN OTHERS;                                      | 2.1 0                                   |

| END dataflow;                                            |                                         |

|                                                          |                                         |

## <section-header>definition of the provide the provid

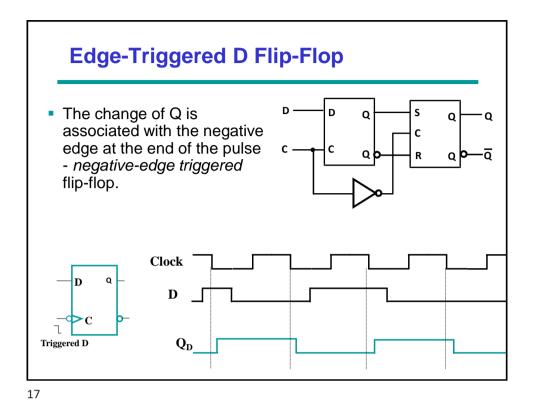

## **Modelling of Flip-Flops**

```

Library IEEE;

use IEEE.Std_Logic_1164.all;

entity FLOP is

port (D, CLK : in std_logic;

Q : out std_logic);

end FLOP;

architecture A of FLOP is

begin

process

begin

wait until CLK'event and CLK=`0';

Q <= D;

end process;

end A;

```

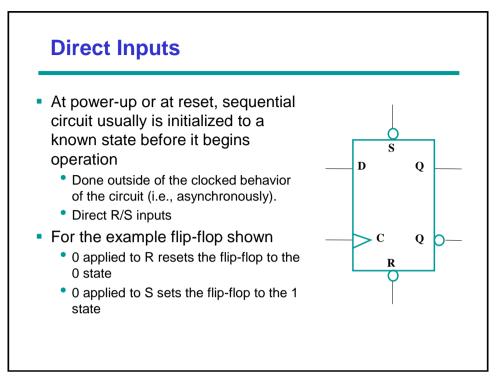

## Positive Edge-triggered D Flip-flop with Asynchronous Set/Reset

```

library IEEE;

use IEEE.std_logic_1164.all;

entity ASYNC FF is

port (D, CLK, SETN, RSTN : in std logic;

Q : out std logic);

end ASYNC FF;

architecture RTL of ASYNC FF is

begin

process (CLK, RSTN, SETN)

begin

if (RSTN = `1`) then

Q <= `0`;

elsif SETN ='1' then

Q <= '1';

elsif (CLK'event and CLK = '1') then

Q <= D;

end if;

end process;

end RTL;

```

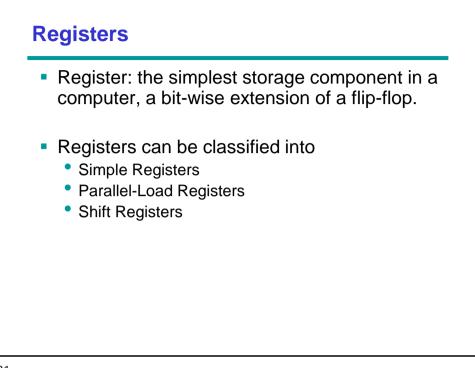

```

Library ieee;

USE ieee.std logic 1164.all;

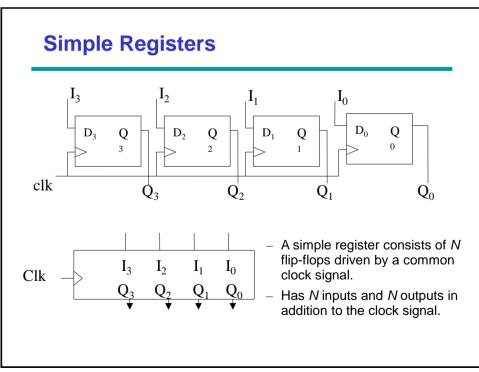

ENTITY simple_register IS

GENERIC ( N : INTEGER := 4);

PORT ( I : IN STD LOGIC VECTOR (N-1 DOWNTO 0);

Clock, Clear, Preset : IN STD_LOGIC;

Q : OUT STD LOGIC VECTOR (N-1 DOWNTO 0));

END simple register;

ARCHITECTURE simple memory OF simple register IS

BEGIN

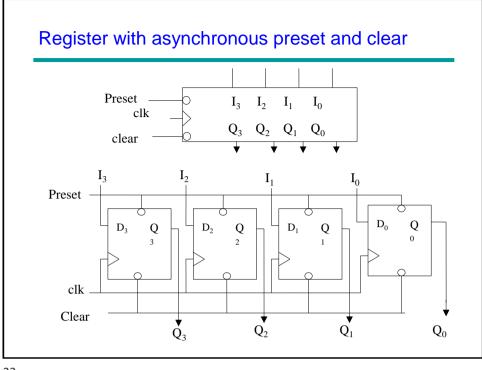

PROCESS (Preset, Clear, Clock)

BEGIN

IF Preset = '0' THEN

Q \ll (OTHERS \implies `l');

ELSIF Clear = '0' THEN

Q <= (OTHERS => '0');

ELSIF (Clock'EVENT AND Clock = '1') THEN

Q <= I;

END IF;

END PROCESS;

END simple_memory;

```

```

25

```

```

Library ieee;

USE ieee.std logic 1164.all;

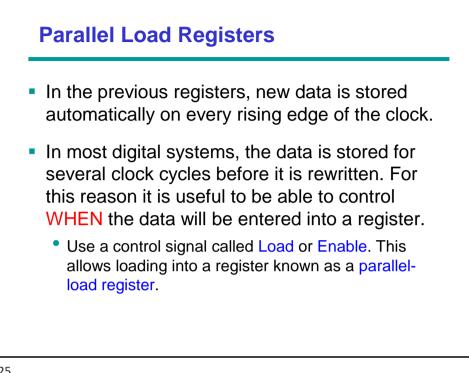

ENTITY load enable IS

GENERIC (N : INTEGER := 4);

PORT ( D : IN STD LOGIC VECTOR (N-1 DOWNTO 0);

Clock, Resetn, load : IN STD LOGIC;

Q : BUFFER STD_LOGIC_VECTOR (N-1 DOWNTO 0));

END load enable;

ARCHITECTURE rtl OF load enable IS

SIGNAL state : std_logic_vector(N-1 DOWNTO 0);

BEGIN

PROCESS (Resetn, Clock) IS

BEGIN

IF Resetn = '0' THEN

state <= (OTHERS => '0');

ELSIF (Clock'EVENT AND Clock = '1') THEN

IF load = '1' THEN

state <= D;</pre>

ELSE

state <= state;</pre>

END IF;

END IF;

END PROCESS;

0 <= state;</pre>

END rtl;

```

## **BCD Counter**

```

architecture Behavioral of bcd_counter is

signal regent : std_logic_vector(3 downto 0);

begin

count: process (reset, clk) is

begin

if ( reset='1' ) then

regent <= "0000";

elsif ( clk'event and clk='1') then

regent <= regent+1;

if (regent = "1001") then

regent <= "0000";

end if;

end if;

end process;

end Behavioral;</pre>

```