EE 459/500 – HDL Based Digital Design with Programmable Logic

Lecture 11 FSM, ASM, FSMD, ASMD

Read before class: Chapters 4,5 from textbook

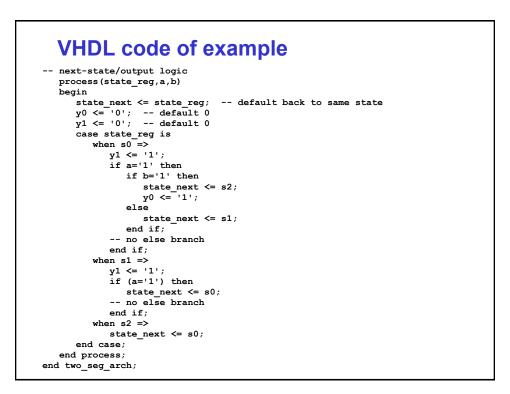

## **VHDL** code of example

```

library ieee;

use ieee.std_logic_1164.all;

```

```

entity fsm_eg is

port(

clk, reset: in std_logic;

a, b: in std_logic;

y0, y1: out std_logic

);

end fsm_eg;

architecture two_seg_arch of fsm_eg is

type eg_state_type is (s0, s1, s2);

signal_state_reg, state_next: eg_state_type;

begin

-- state register

process(clk,reset)

begin

if (reset='1') then

state_reg <= s0;</pre>

elsif (clk'event and clk='1') then

state_reg <= state_next;</pre>

end if;

end process;

```

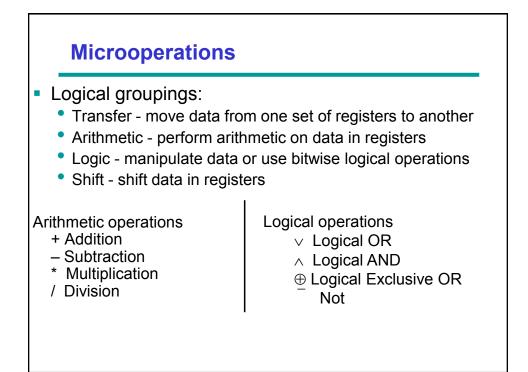

| Symbolic Designation                   | Description            |

|----------------------------------------|------------------------|

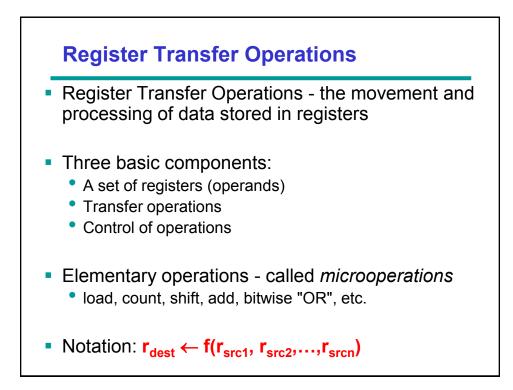

| $R0 \leftarrow R1 + R2$                | Addition               |

| $R0 \leftarrow \overline{R1}$          | Ones Complement        |

| $R0 \leftarrow \overline{R1} + 1$      | Two's Complement       |

| $R0 \leftarrow R2 + \overline{R1} + 1$ | R2 minus R1 (2's Comp) |

| $R1 \leftarrow R1 + 1$                 | Increment (count up)   |

| $R1 \leftarrow R1 - 1$                 | Decrement (count down) |

These simple microoperations operate on the whole word

| Symbolic                                              | Description                     |

|-------------------------------------------------------|---------------------------------|

| Designation                                           | 2 esemption                     |

| $R0 \leftarrow \overline{R1}$                         | Bitwise NOT                     |

| $\mathbf{R0} \leftarrow \mathbf{R1} \lor \mathbf{R2}$ | Bitwise OR (sets bits)          |

| $R0 \leftarrow R1 \land R2$                           | Bitwise AND (clears bits)       |

| $R0 \leftarrow R1 \oplus R2$                          | Bitwise EXOR (complements bits) |

| ift Microop<br>R2 = 110010 |             |            |

|----------------------------|-------------|------------|

|                            | 1           | -          |

| Symbolic<br>Designation    | Description | R1 content |

| R1 ← sl R2                 | Shift Left  | 10010010   |

|                            | Shift Right | 01100100   |

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

VHDL code

entity fib is

port(

clk, reset: in std_logic;

start: in std_logic;

i: in std_logic_vector(4 downto 0);

ready, done_tick: out std_logic;

f: out std_logic_vector(19 downto 0)

);

end fib;

architecture arch of fib is

chitecture arch of fib is

type state_type is (idle,op,done);

signal state_reg, state_next: state_type;

signal t0_reg, t0_next, t1_reg, t1_next: unsigned(19 downto 0);

signal n_reg, n_next: unsigned(4 downto 0);

begin

-- fsmd state and data registers

process (clk, reset)

begin

if reset='1' then

if reset='1 then

state_reg <= idle;

t0_reg <= (others=>'0');

t1_reg <= (others=>'0');

n_reg <= (others=>'0');

elsif (clk'event and clk='1') then

state_reg <= state_next;

t0_reg <= t0_next;

t1_reg <= t1_next;

n_reg <= n_next;</pre>

end if;

end process;

```

```

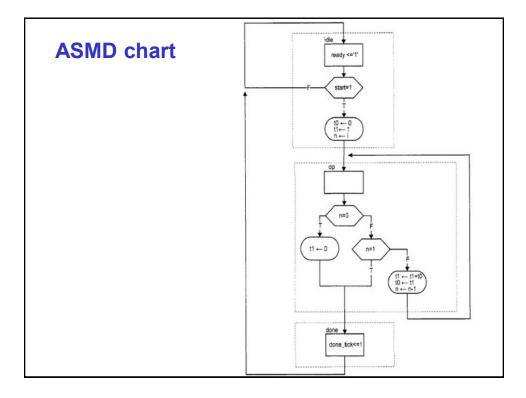

fsmd next-state logic

process(state_reg,n_reg,t0_reg,t1_reg,start,i,n_next)

begin

.

ready <='0';

done_tick <= '0';</pre>

state next <= state reg;</pre>

t0_next <= t0_reg;

t1_next <= t1_reg;</pre>

n next <= n reg;

case state_reg is

when idle =>

ready <= '1';

if start='1' then

t0_next <= (others=>'0');

t1 next <= (0=>'1', others=>'0');

n_next <= unsigned(i);</pre>

state_next <= op;</pre>

end if;

when op =>

if n_reg=0 then

t1_next <= (others=>'0');

state_next <= done;</pre>

elsif n_reg=1 then

state_next <= done;</pre>

else

t1_next <= t1_reg + t0_reg;

t0_next <= t1_reg;

n_next <= n_reg - 1;</pre>

end if;

when done =>

done tick <= '1';</pre>

state_next <= idle;</pre>

end case:

end process;

-- output

f <= std_logic_vector(t1_reg);</pre>

end arch;

```