# COEN-4730 Computer Architecture Info on GEM5, McPAT, and More

Cristinel Ababei Dept. of Electrical and Computer Engineering Marquette University

| GEM5 Resources                                                                |  |

|-------------------------------------------------------------------------------|--|

| <u>http://www.m5sim.org/Tutorials</u>                                         |  |

| http://www.m5sim.org/Documentation                                            |  |

| <ul> <li>http://www.m5sim.org/wiki/index.php/Tutorials</li> </ul>             |  |

| <ul> <li>http://www.gem5.org/dist/tutorials/isca_pres_2011.pdf</li> </ul>     |  |

| <ul> <li>http://gem5.org/dist/tutorials/hipeac2012/gem5_hipeac.pdf</li> </ul> |  |

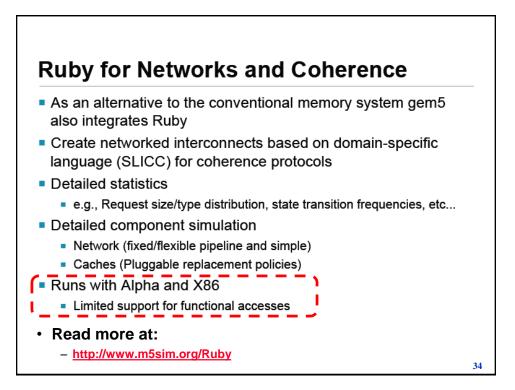

| <u>http://www.m5sim.org/Ruby</u>                                              |  |

| GEMS Resources                                                                |  |

| http://research.cs.wisc.edu/gems/                                             |  |

| http://lists.cs.wisc.edu/mailman/listinfo/gems-users                          |  |

| You can find (some) answers at:                                               |  |

| - http://blog.gmane.org/gmane.comp.emulators.m5.users                         |  |

| http://www.mail-archive.com/gem5-users@gem5.org/                              |  |

| – <u>http://www.m5sim.org/Frequently_Asked_Questions</u>                      |  |

| http://ga.gem5.org/                                                           |  |

| Check periodically the status matrix of GEM5:                                 |  |

| http://www.m5sim.org/Status_Matrix                                            |  |

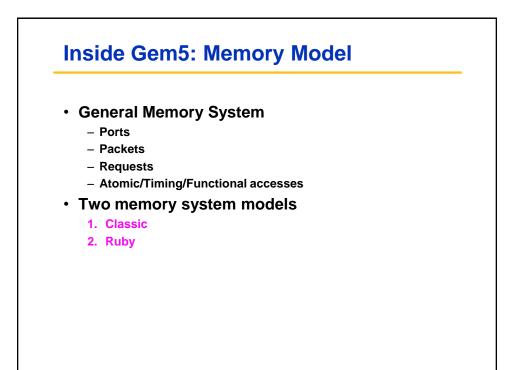

## GEM5 = M5 + GEMS (i.e., Ruby only)

### • **GEM5**

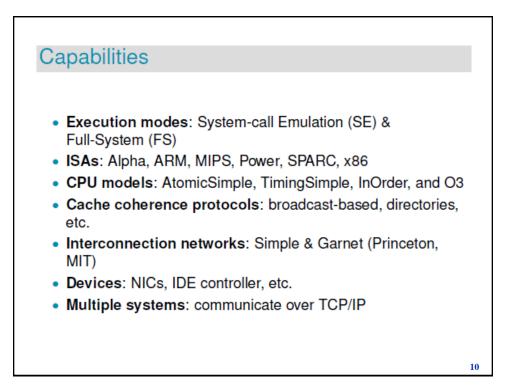

- Supports both functional and timing simulation

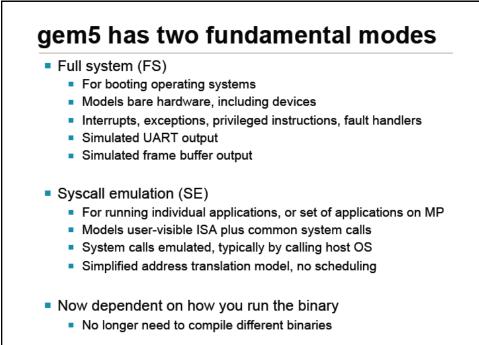

- Has two simulation modes: full-system (FS) and syscall emulation (SE)

- Supports multiple ISAs

- » ALPHA: well-developed to support both FS and SE modes

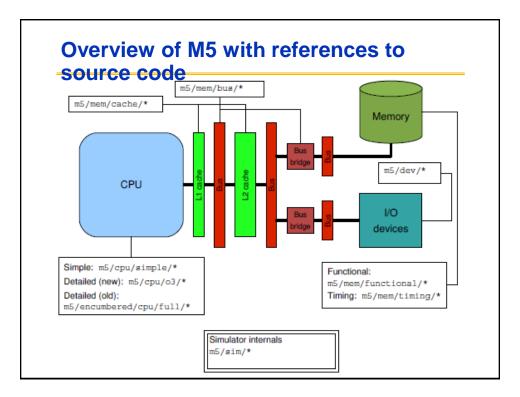

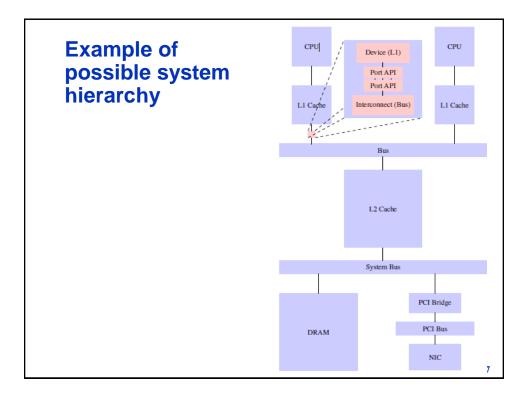

- It models

- » Processor Cores + Memory Hierarchy + I/O Systems

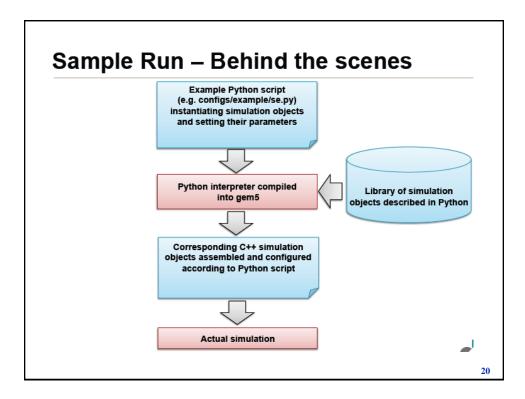

- Written by using C++, Python & Swig, and totally open-source

- More things about M5

- http://www.m5sim.org/wiki/index.php/Main\_Page

- The most important document: http://www.m5sim.org/wiki/index.php/Tutorials

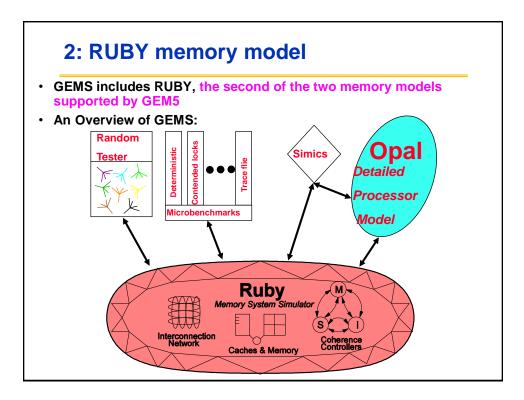

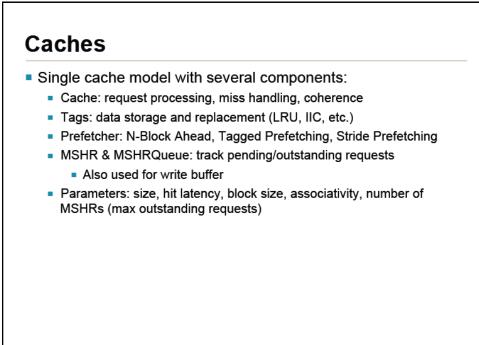

- Domain-Specific Language

- Syntatically similar to C/C++

- Like HDLs, constrains operations to be hardware-like (e.g., no loops)

- Two generation targets

- C++ for simulation

- » Coherence controller object

- HTML for documentation

- » Table-driven specification (State x Event -> Actions & next state)

#### 49

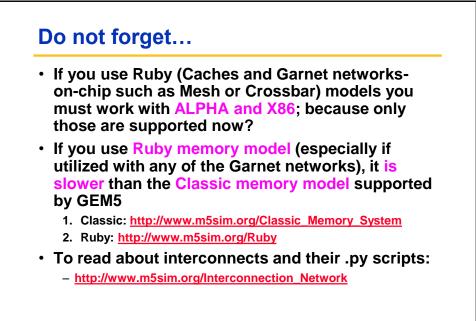

### Do not forget...

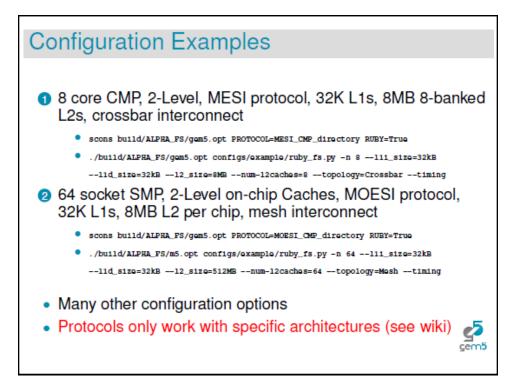

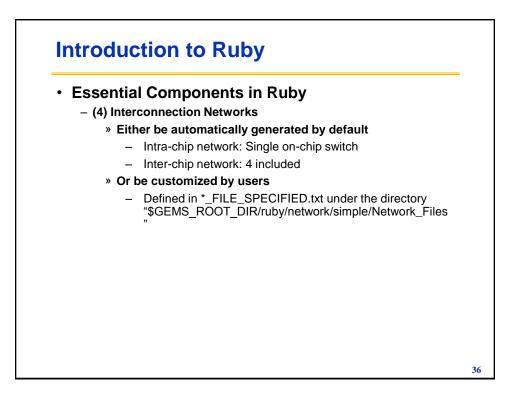

Mesh network:

- This topology requires the number of directories to be equal to the number of CPUs.

- It can be invoked from command line by --topology=Mesh.

- The number of routers/switches is equal to the number of CPUs in the system.

- The number of rows in the mesh has to be specified by --mesh-rows.

- Each router/switch is connected to one L1, one L2 (if present), and one Directory.

### Do not forget...

- How many CPUs can M5 run?

- There is no inherent limit in M5 (other than simulation speed). In SE mode there are no obstacles to simulating as many CPUs as you want. However, in FS mode, the real-world Alpha platform we model (Tsunami) only supports up to 4 processors. To get around this limit, we defined and implemented a variant of the Tsunami platform (which we call BigTsunami) that can take up to 64 processors. Note that BigTsunami does not correspond to any real system. BigTsunami support is included in the standard M5 Alpha build, but booting with more than 4 CPUs requires modifications to the PAL code and kernel as well. Take a look at the Download page for our Linux patches and modified PAL code. Note that even with the BigTsunami changes, simulating 64 processors will be quite slow, and the Linux scheduler doesn't seem particularly good at scheduling a large number of processors.

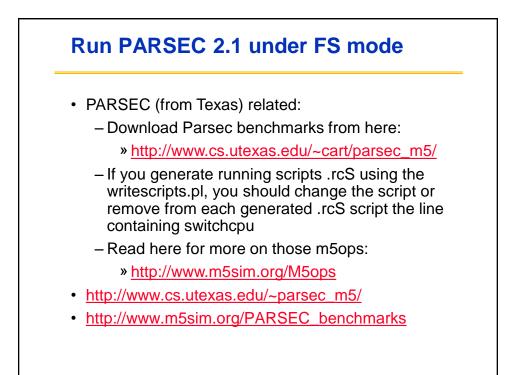

- Prebuilt kernel and PAL binaries can be found at: <u>http://www.cs.utexas.edu/~cart/parsec\_m5/</u>