| Quest for DRAM Performance                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| <ul> <li>1. Fast Page mode         <ul> <li>Add timing signals that allow repeated accesses to row buffer with another row access time</li> <li>Such a buffer comes naturally, as each array will buffer 1024 to 204 for each access</li> </ul> </li> </ul>                                                                                                                                                                                        |          |

| <ul> <li>2. Synchronous DRAM (SDRAM)</li> <li>° Add a clock signal to DRAM interface, so that repeated transfers w bear overhead to synchronize with DRAM controller</li> </ul>                                                                                                                                                                                                                                                                    | ould not |

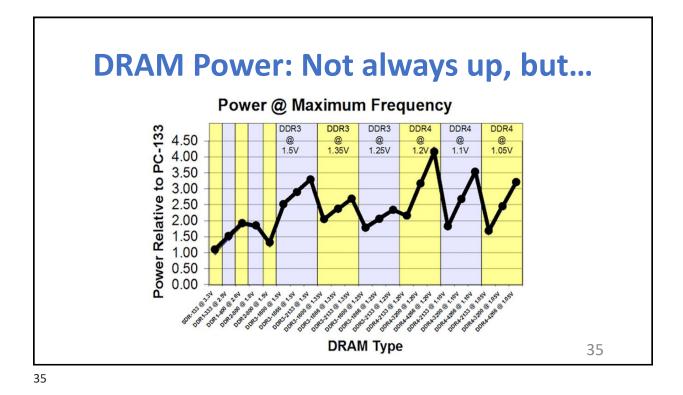

| <ul> <li>3. Double Data Rate (DDR SDRAM)         <ul> <li>Transfer data on both the rising edge and falling edge of the DRAM signal ⇒ doubling the peak data rate</li> <li>DDR2 lowers power by dropping the voltage from 2.5 to 1.8 volts + higher clock rates: up to 400 MHz</li> <li>DDR3 drops to 1.5 volts + higher clock rates: up to 800 MHz</li> <li>DDR4 drops to 1-1.2 volts + higher clock rates: up to 1600 MHz</li> </ul> </li> </ul> | I clock  |

|                 | Memory Optimizations |           |               |                  |            |            |  |  |  |

|-----------------|----------------------|-----------|---------------|------------------|------------|------------|--|--|--|

|                 |                      |           |               |                  |            |            |  |  |  |

|                 |                      |           | Best case ac  | Precharge needed |            |            |  |  |  |

| Production year | Chip size            | DRAM type | RAS time (ns) | CAS time (ns)    | Total (ns) | Total (ns) |  |  |  |

| 2000            | 256M bit             | DDR1      | 21            | 21               | 42         | 63         |  |  |  |

| 2002            | 512M bit             | DDR1      | 15            | 15               | 30         | 45         |  |  |  |

| 2004            | 1G bit               | DDR2      | 15            | 15               | 30         | 45         |  |  |  |

| 2006            | 2G bit               | DDR2      | 10            | 10               | 20         | 30         |  |  |  |

| 2010            | 4G bit               | DDR3      | 13            | 13               | 26         | 39         |  |  |  |

| 2016            | 8G bit               | DDR4      | 13            | 13               | 26         | 39         |  |  |  |

## **Memory Optimizations**

| StandardI/O clock rateDDR1133 |      | M transfers/s | DRAM name | MiB/s/DIMM | DIMM name<br>PC2100 |  |

|-------------------------------|------|---------------|-----------|------------|---------------------|--|

|                               |      | 266           | DDR266    | 2128       |                     |  |

| DDR1                          | 150  | 300           | DDR300    | 2400       | PC2400              |  |

| DDR1                          | 200  | 400           | DDR400    | 3200       | PC3200              |  |

| DDR2                          | 266  | 533           | DDR2-533  | 4264       | PC4300              |  |

| DDR2                          | 333  | 667           | DDR2-667  | 5336       | PC5300              |  |

| DDR2                          | 400  | 800           | DDR2-800  | 6400       | PC6400              |  |

| DDR3                          | 533  | 1066          | DDR3-1066 | 8528       | PC8500              |  |

| DDR3                          | 666  | 1333          | DDR3-1333 | 10,664     | PC10700             |  |

| DDR3                          | 800  | 1600          | DDR3-1600 | 12,800     | PC12800             |  |

| DDR4                          | 1333 | 2666          | DDR4-2666 | 21,300     | PC21300             |  |

33

|                |                  |         |            | pni                 | CS      | IVI     | en       | nory          |                 |                                                            |                    |

|----------------|------------------|---------|------------|---------------------|---------|---------|----------|---------------|-----------------|------------------------------------------------------------|--------------------|

| Product        | Density          | Banks   | Part Num.  | PKG & Speed         | Org.    | Interf. | Ref.     | Voltage(V)    | PKG.            | PKG Type                                                   | Status             |

| gDDR3<br>SDRAM | 1Gb G-die        |         | K4W1G1646G | BC08/1A<br>11/12/15 | 64Mx16  |         |          | 1.5V ± 0.075V | 96ball<br>FBGA  | Halogen-Free,<br>Lead-Free<br>& Flip-Chip                  | Mass<br>Production |

|                | 2Gb C-die        | 8Banks  | K4W2G1646C | HC1A/11<br>12/15    | 128Mx16 |         |          |               |                 | Halogen-Free<br>& Lead-Free<br>Halogen-Free<br>& Lead-Free | Mass<br>Production |

|                | DDP<br>4Gb D-die |         | K4W4G1646D | BC12                | 256Mx16 |         |          |               |                 |                                                            | CS<br>Jan.'11      |

| GDDR3<br>SGRAM | 512Mb I-die      | 8Banks  | K4J52324KI | HC7A/08<br>1A/12/14 | 16Mx32  | POD_18  |          | 1.8V±0.1V     | 136ball<br>FBGA |                                                            | Mass<br>Production |

|                | 1Gb G-die        |         | K4J10324KG | HC1A/14             | 32Mx32  |         |          |               |                 |                                                            | CS<br>Aug.'11      |

| GDDR5<br>SGRAM | 1Gb G-die        | 16Banks | K4G10325FG | HC03/04/05          | 32Mx32  | POD_15  | 8K/32ms  | 1.5V ± 0.045V | 170ball<br>FBGA | Halogen-Free<br>& Lead-Free                                | Mass<br>Production |

|                | 2Gb C-die        |         | K4G20325FC | HC03/04/05          | 64Mx32  | POD_15  | 16K/32ms | 1.5V ± 0.045V | 170ball<br>FBGA | Halogen-Free<br>& Lead-Free                                | Mass<br>Production |

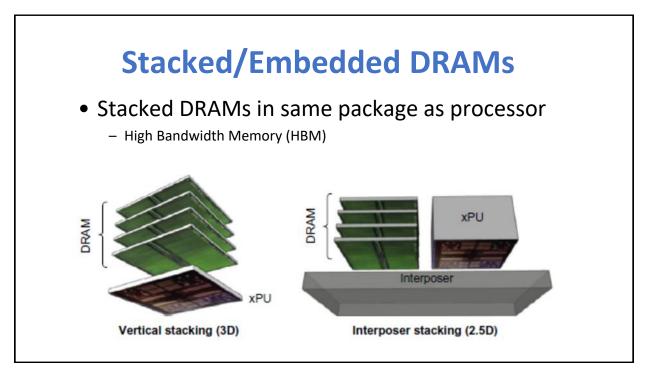

## • Achieve 2-5 X bandwidth per DRAM vs. DDR3

° Wider interfaces (32 vs. 16 bit)

° Higher clock rate

· Possible because they are attached via soldering instead of socketted DIMM modules

° E.g. Samsung GDDR5

• 2.5GHz, 20 GBps bandwidth on 32-bit bus (160GBps on 256-bit bus)

34

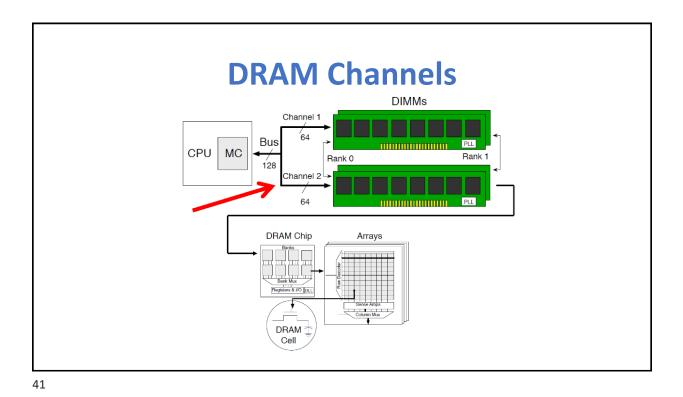

## **Increasing Capacity: Multiple DIMMs on a Channel** Rank 1 Rank 2 Rank 3 Rank 4 Advantages ° Enables even capacity Single Disadvantages Channel SDRAM ° Interconnect latency Controller ° Complexity ° Higher energy usage <sup>o</sup> Address/Command signal integrity is a challenge Addr & Cmd Data Bus "Mesh Topology" Chip (DIMM) Select 40

## **Mobile DRAM characteristics** LPDDR2 **Technology Parameter** DDR3 Timing (tCAS, tRAS, tRC) 15, 38, 50ns 15, 42, 57ns 210, 175mA Active current (Read, Write) 180.185mA Idle current (Powerdown, Standby) 35,45mA 1.6, 23mA Powerdown exit latency 7.5ns 24ns 1.5V 1.2V Operating voltage 800MHz 400MHz Typical operating frequency Device width 8 16 Same core as DDR3 devices ° Same capacity per device, same access latency, same active currents IO interface optimized for very low static power ° Including faster power down modes, no termination • Same chip bandwidth ° Wider interface operating at slower clock rate 61